Which one of the following statements is FALSE? The TLB performs an associative search in parallel on all its valid entries using page number of incoming virtual address. If the virtual address of a word given by CPU has a TLB hit, but the subsequent search for the word results in a cache miss, then the word will always be present in the main memory The memory access time using a given inverted page table is always same for all incoming virtual addresses. In a system that uses hashed page tables, if two distinct virtual addresses V1 and V2 map to the same value while hashing, then the memory access time of these addresses will not be the same No, the answer is incorrect. Score: 0 Accepted Answers: The memory access time using a given inverted page table is always same for all incoming virtual addresses. Gate Mock Test, Gate Practice Test question, Answer carefully with all clear steps and accuracy with given answer:17) Which on of the following statements is FALSE? zpos “The TL8 performs an associative search in parallel on all is valk entries using page number of incoming virtua adress. the vial address ofa word given by CPL has TLE hi, but the subsequent search fo the word esuls i cache miss, the the word willabiays be present nthe main memory “The memory access ime using given inverted page table is always same or al ncoming vital adresses. na system tha uses hashed page tables, two distinct vial addresses V1 and V2 map to th same vale whi hashing, then the memory access ime of thse addresses will ot be the same No, the answer is Incorrect, Seore:0 Accepted Answers: The memory acess mousing a genera page alos aba same fr a ncomin vital adksses.

Question:

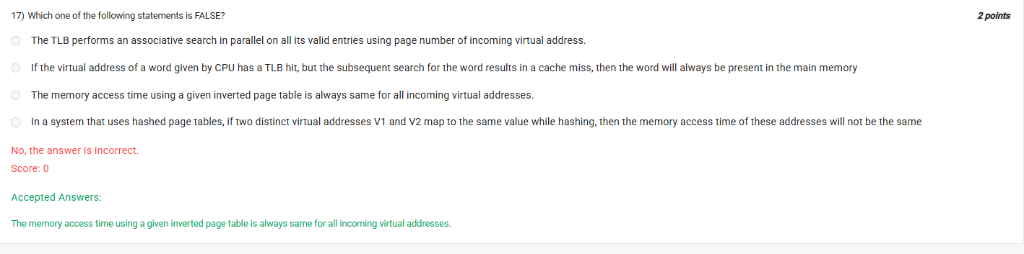

Which one of the following statements is FALSE?

The TLB performs an associative search in parallel on all its valid entries using page number of incoming virtual address.

If the virtual address of a word given by CPU has a TLB hit, but the subsequent search for the word results in a cache miss, then the word will always be present in the main memory

The memory access time using a given inverted page table is always same for all incoming virtual addresses.

In a system that uses hashed page tables, if two distinct virtual addresses V1 and V2 map to the same value while hashing, then the memory access time of these addresses will not be the same

No, the answer is incorrect.

Score: 0

Accepted Answers:

The memory access time using a given inverted page table is always same for all incoming virtual addresses.

Gate Mock Test, Gate Practice Test question, Answer carefully with all clear steps and accuracy with given answer: 17) Which on of the following statements is FALSE? zpos

“The TL8 performs an associative search in parallel on all is valk entries using page number of incoming virtua adress.

the vial address ofa word given by CPL has TLE hi, but the subsequent search fo the word esuls i cache miss, the the word willabiays be present nthe main memory

“The memory access ime using given inverted page table is always same or al ncoming vital adresses.

na system tha uses hashed page tables, two distinct vial addresses V1 and V2 map to th same vale whi hashing, then the memory access ime of thse addresses will ot be the same

No, the answer is Incorrect,

Seore:0

Accepted Answers:

The memory acess mousing a genera page alos aba same fr a ncomin vital adksses.

17) Which on of the following statements is FALSE? zpos

“The TL8 performs an associative search in parallel on all is valk entries using page number of incoming virtua adress.

the vial address ofa word given by CPL has TLE hi, but the subsequent search fo the word esuls i cache miss, the the word willabiays be present nthe main memory

“The memory access ime using given inverted page table is always same or al ncoming vital adresses.

na system tha uses hashed page tables, two distinct vial addresses V1 and V2 map to th same vale whi hashing, then the memory access ime of thse addresses will ot be the same

No, the answer is Incorrect,

Seore:0

Accepted Answers:

The memory acess mousing a genera page alos aba same fr a ncomin vital adksses.

Asked by: Vishal

Created at: 2025-11-05 13:58:39

Final Answer:

📢 Instructions:

- Ask anything relatd to above question only.

- For new Question goto :

VIPSolutions

VIPSolutions